Chiplet先进封装设计与验证

Chiplet Advanced Packaging Design and Verification

产品介绍

按照SoC发展的趋势,Chiplet架构已成为芯片与系统设计不可替代的后摩尔方案,特别是在高性能计算、5G通信及智能设备等领域,以3D设计为代表的先进封装芯粒集成能够提供更大的设计灵活性和更高的集成度。

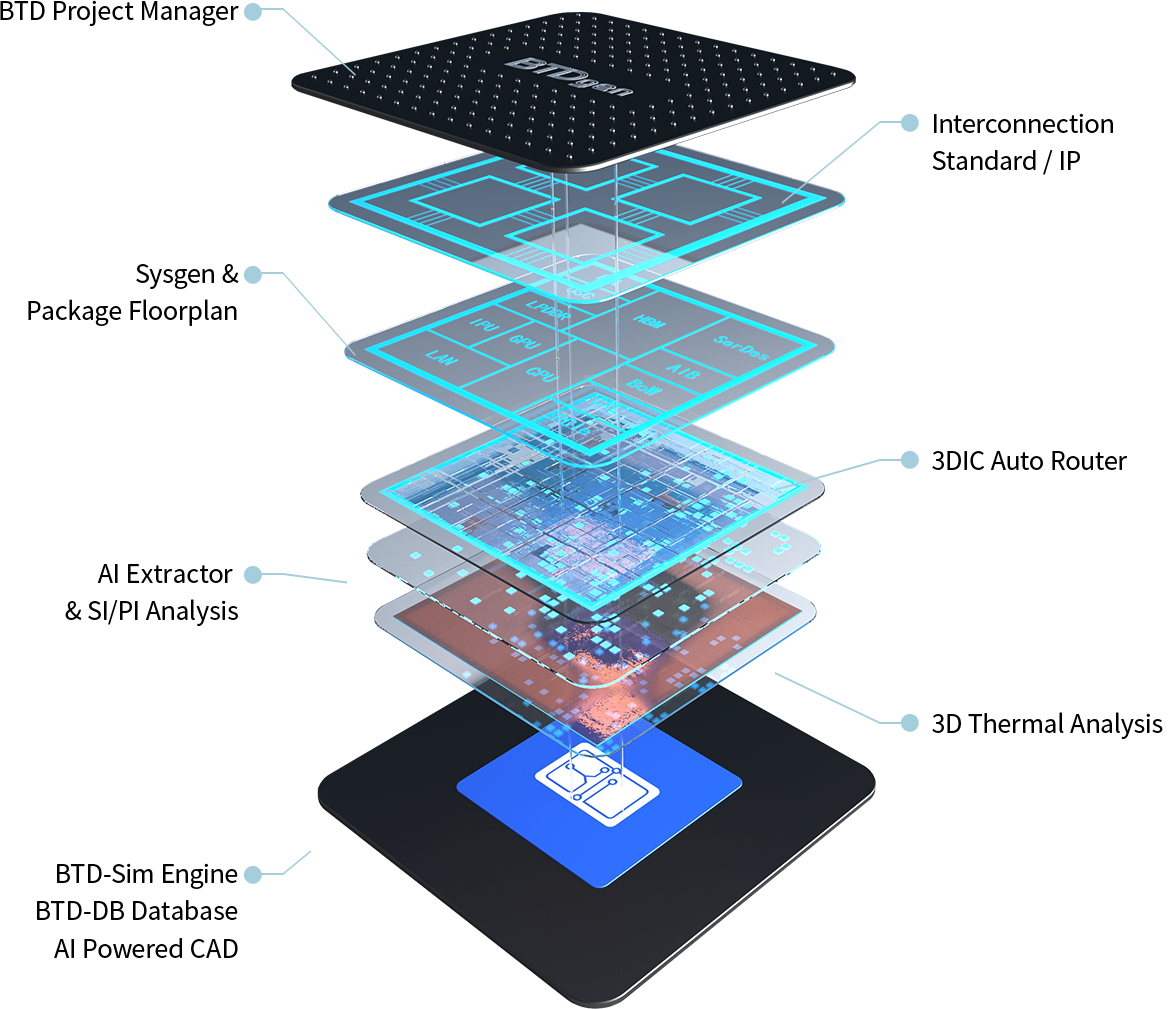

BTDgen是比昂芯科技自主研发的Chiplet大规模集成设计与验证平台,提供裸片到裸片(D2D)的先进封装设计,现版本用于完成3D硅中介层、硅基板RDL层的高密度互连布线,包括微凸点、C4、BGA和I/O等。本设计平台的核心技术涵盖了前端系统规划、物理设计核心流程、基于AI的参数提取、系统级信号链分析和多物理场协同仿真等,可显著缩短Chiplet架构异构集成芯片的设计周期,达到需要的设计精度。

主要特点

全流程模块化可扩展

- 基于可收敛验证的2.5D集成实现

- 提供可定制和扩展的工具架构

- 支持定制,根据实际需求优化工具使用

原生数据底座管理参数

- 跨层级互连线提取

- 统一数据底座,集中管理设计数据

封装与接口设计

- 专为Chiplet架构优化的封装设计工具

- 支持高速接口设计和多层封装方案

- 支持高频通信和复杂信号

兼容主流EDA工具

- 与业界主流工具(如APD、Virtuoso等)无缝对接

- 兼容现有设计流程,确保数据的顺畅流转与互操作性

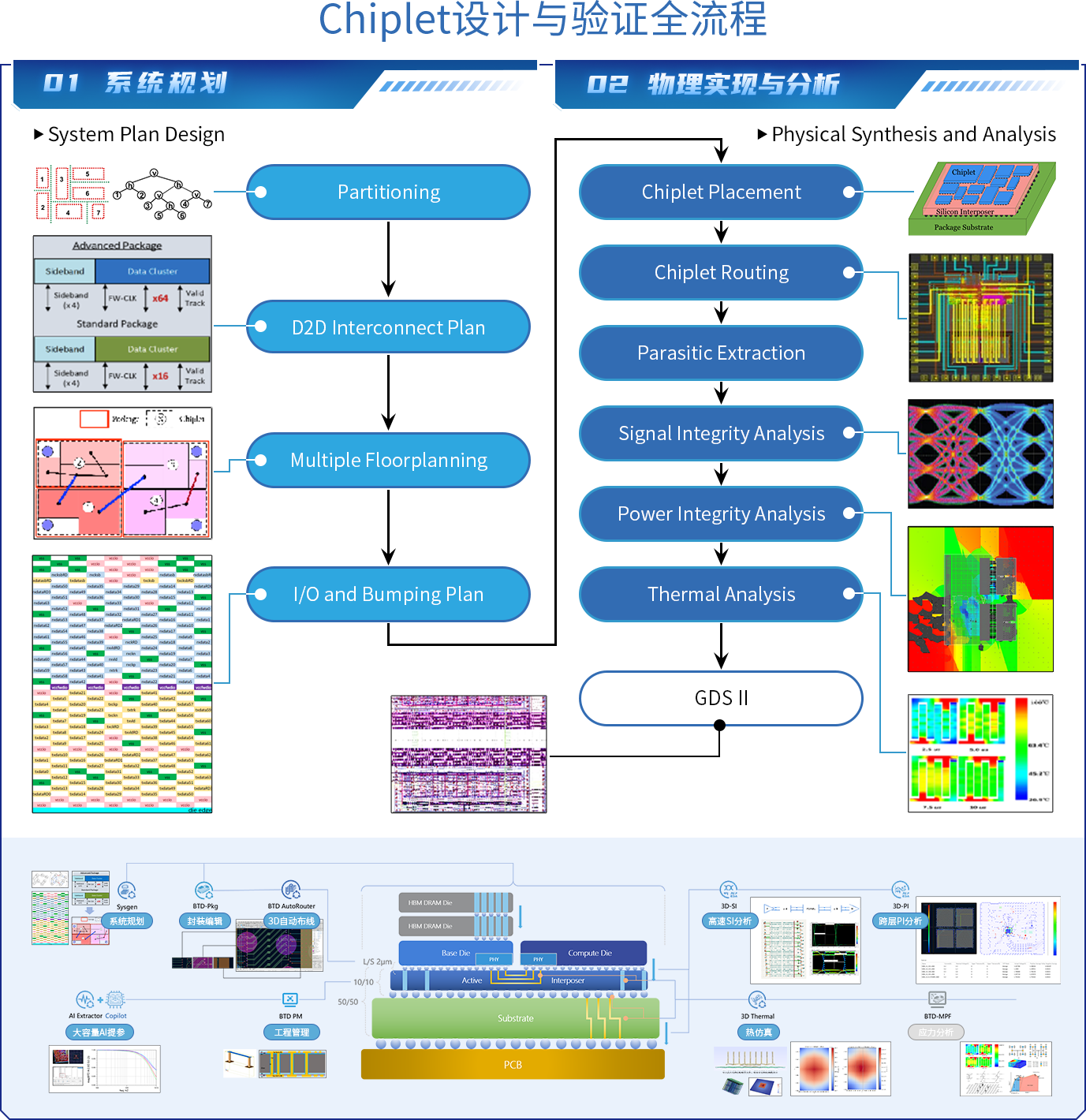

设计流程

芯粒设计追求良率、IP复用、性能和成本优化的显著价值。将具有不同或相同功能的多个芯粒集成到单个封装中产生更高密度互连和更大面积的先进封装的需求,如何优化布局、快速收敛物理设计与电性和多物理仿真,以完成Chiplet产品的设计变得非常关键。

BTDgen现版本实现2.5D先进封装的设计与优化,为工程师提供从芯片布局到物理验证的全流程解决方案。设计与验证全流程功能覆盖从系统生成、版图设计到布局布线和电热仿真,无论是模块间互联、自动布线、电源优化,还是验证仿真,BTDgen均有特色功能高效可靠地完成,帮助设计团队解决设计瓶颈,缩短产品研发周期。