Chiplet先进封装设计与验证

Chiplet Advanced Packaging Design and Verification

产品介绍

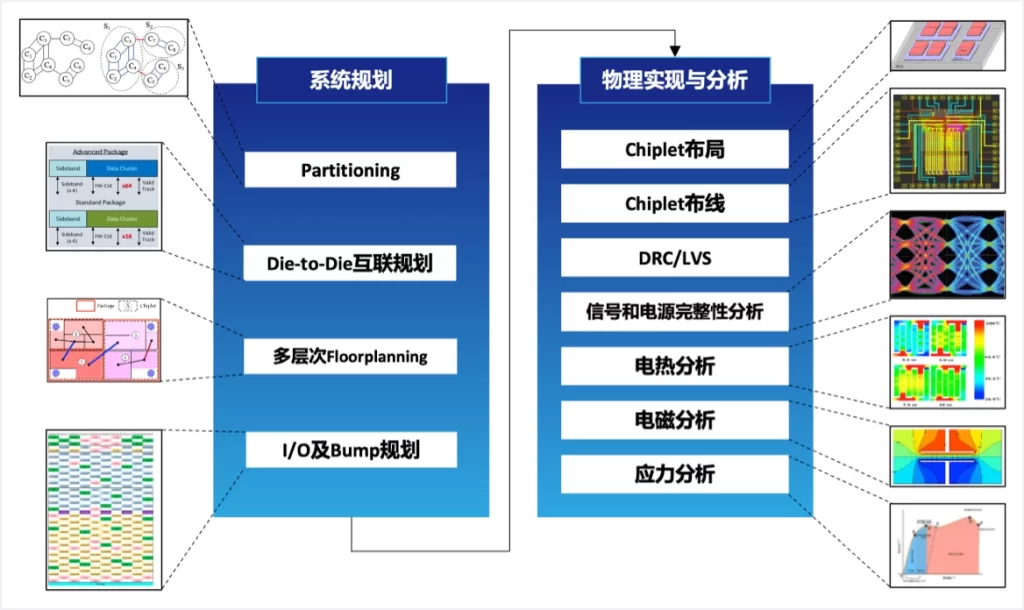

BTD-Chiplet物理设计核心流程

首创集成设计和验证融合全流程

- 版图设计自动化 + SI/PI + 电热验证

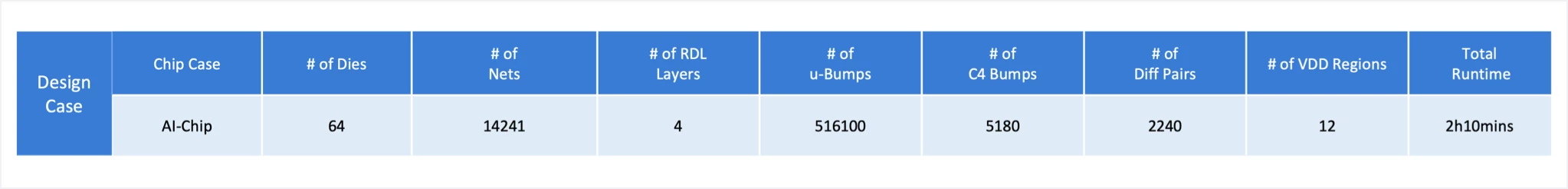

集成设计加速

- 海外工具:超2个月(布通率低,工具不集成)

- BTD工具:2h10mins(高布通率,集成工具)

- 案例:64芯粒、14k互联、类脑芯片

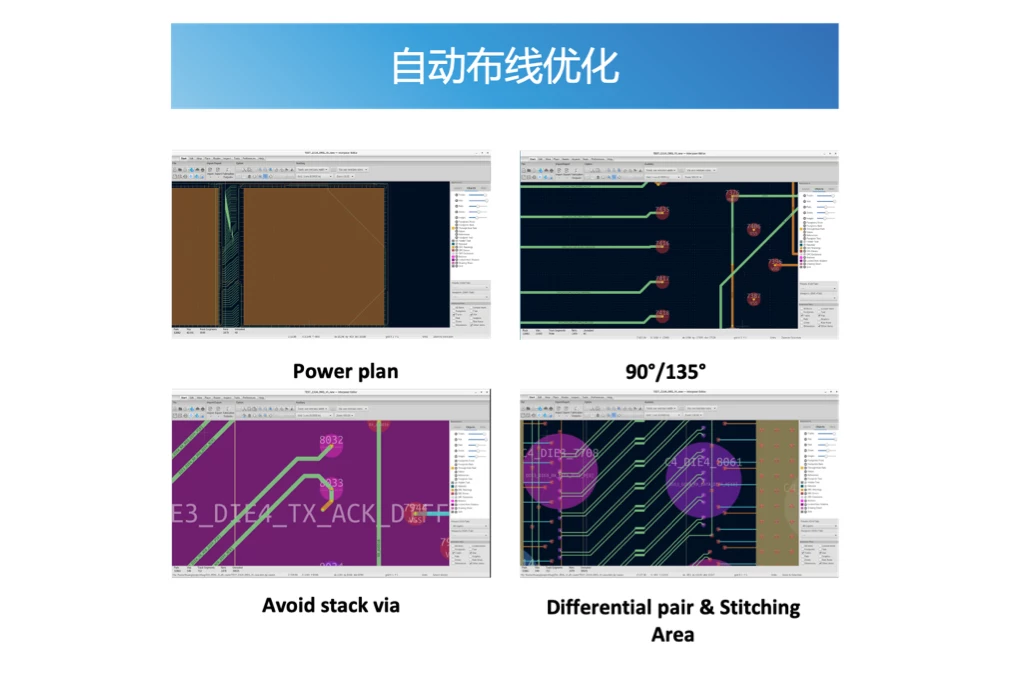

- 支持P/G网络的供电平板的生成

- 支持90°/135°的走线设计

- 支持堆叠孔的定制化,可选择打孔方式为avoid stack via

- 支持差分对布线

- 支持stitching的区域指定

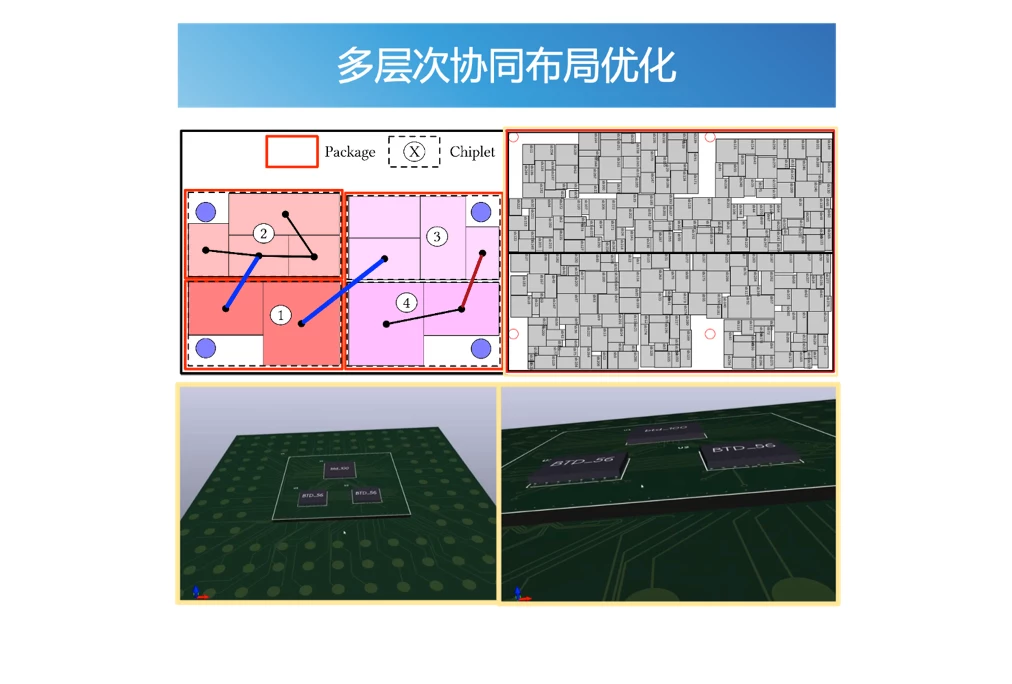

- 支持多封装系统的协同优化

- 支持从Chiplet到PCB的多层次优化

- 支持Partitioning与Floor planning的协同优化

- 支持多种封装结构: 2.5D, M3D , ...

- 支持多物理模型的协同优化

- 支持早期的可布线性优化

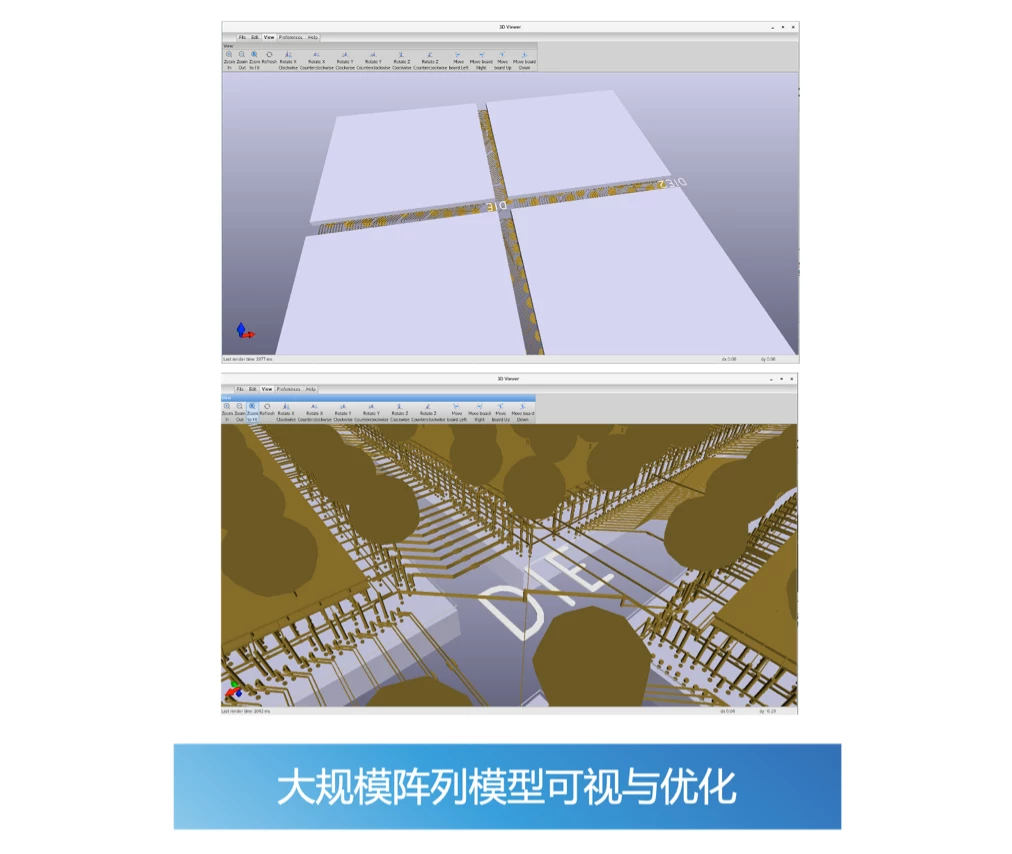

- 支持对结构二维2D及三维3D可视化

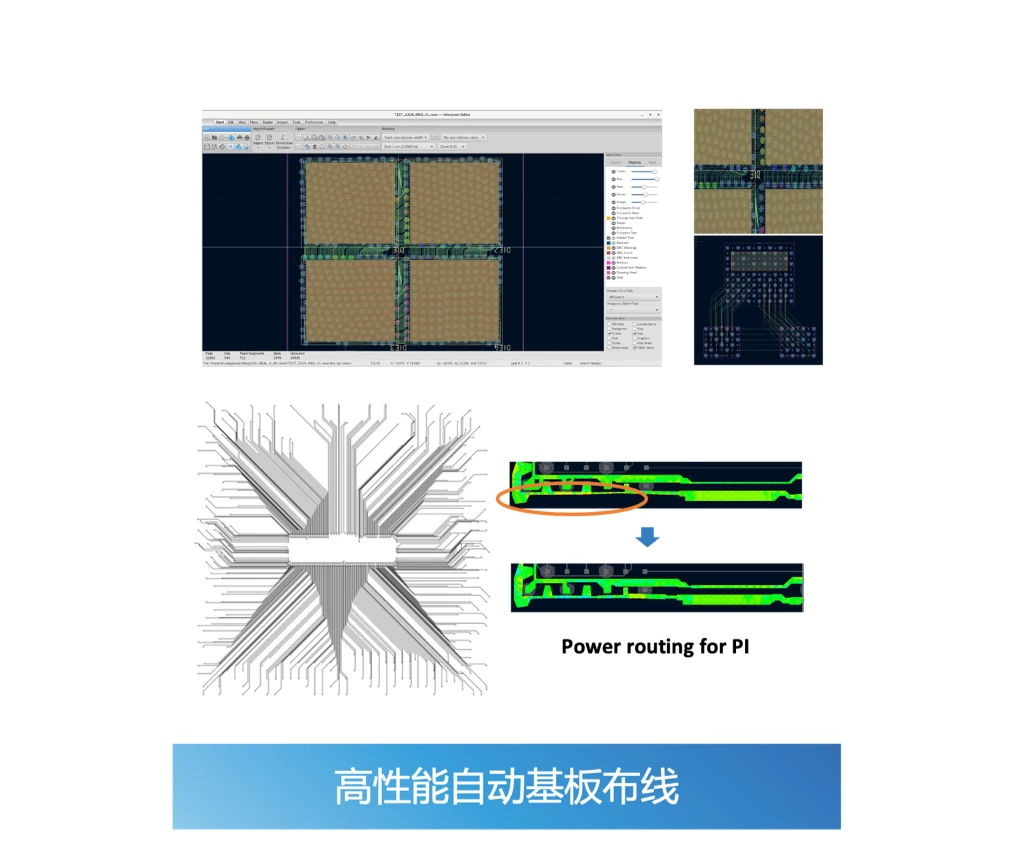

- 支持高性能RDL/PCB布线

- 支持Escape Routing与Area Routing的协同优化

- 提供满足用户需求的自动布线优化

- 支持多种类型版图的自动布线

- 支持RDL布线和PCB布线的协同优化

- 可针对不同设计规则进行专门优化

- 3D模型生成和高效渲染

- 超大规模设计,各部件细节高效显示

- 系统显示和细节显示无障碍切换

- 组件分离设置

- 任意自由度交互

- 渲染可定制化设置